VSync 信號會同步處理顯示管道。顯示管道包含應用程式轉譯、SurfaceFlinger 合成,以及 Hardware Composer (HWC) 在螢幕上顯示圖片。VSync 會同步處理應用程式喚醒以開始轉譯的時間、SurfaceFlinger 喚醒以組合畫面的時間,以及螢幕更新週期。這項同步功能可消除畫面延遲,並提升圖像的視覺效能。

HWC 會產生 VSync 事件,並透過回呼將事件傳送至 SurfaceFlinger:

typedef void (*HWC2_PFN_VSYNC)(hwc2_callback_data_t callbackData, hwc2_display_t display, int64_t timestamp);

SurfaceFlinger 會呼叫 setVsyncEnabled,藉此控管 HWC 是否要產生 VSync 事件。SurfaceFlinger 可讓 setVsyncEnabled 產生 VSync 事件,以便與螢幕的重新整理週期同步。當 SurfaceFlinger 同步處理顯示器重新整理週期時,SurfaceFlinger 會停用 setVsyncEnabled,停止 HWC 產生 VSync 事件。如果 SurfaceFlinger 偵測到實際 VSync 與先前建立的 VSync 有差異,SurfaceFlinger 會重新啟用 VSync 事件產生功能。

VSync 偏移

同步應用程式和 SurfaceFlinger 會將迴圈算繪至硬體 VSync。在 VSync 事件中,螢幕開始顯示影格 N,而 SurfaceFlinger 則開始組合影格 N+1 的視窗。應用程式會處理待處理的輸入內容,並產生影格 N+2。

與 VSync 同步處理可確保延遲時間一致。這項功能可減少應用程式和 SurfaceFlinger 中的錯誤,並盡量避免螢幕彼此間的相位漂移。前提是應用程式和 SurfaceFlinger 的每影格時間不會有太大差異。延遲時間至少為兩個影格。

為解決這個問題,您可以運用 VSync 偏移量,將應用程式和合成信號設為與硬體 VSync 相關,藉此縮短輸入到顯示的延遲時間。這是因為應用程式加上組合通常不到 33 毫秒。

VSync 偏移的結果是三個信號,具有相同的週期和偏移相位:

HW_VSYNC_0- 螢幕開始顯示下一個影格。VSYNC- 應用程式讀取輸入內容並產生下一個影格。SF_VSYNC- SurfaceFlinger 開始合成下一個影格。

有了 VSync 偏移,SurfaceFlinger 就能在應用程式同時處理輸入內容並轉譯影格時,接收緩衝區並合成影格。

DispSync

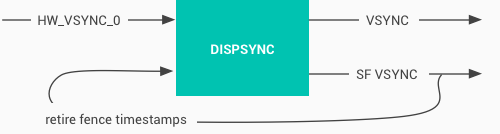

DispSync 會維護螢幕的週期性硬體 VSync 事件模型,並使用該模型在硬體 VSync 事件的特定階段偏移執行回呼。

DispSync 是軟體鎖相迴路 (PLL),可產生 Choreographer 和 SurfaceFlinger 使用的 VSYNC 和 SF_VSYNC 訊號,即使未從硬體 VSync 偏移也一樣。

DispSync 流程如下圖所示:

圖 1. DispSync 流程。

DispSync 具有下列特質:

- 參考資料 -

HW_VSYNC_0。 - 輸出 -

VSYNC和SF_VSYNC。 - 意見回饋:從 HWC 淘汰圍欄信號時間戳記。

VSync 退休偏移

即使在未使用偏移階段的裝置上,退除柵欄的信號時間戳記也必須與硬體 VSync 相符。否則,錯誤的嚴重程度可能會比實際情況更嚴重。智慧面板通常會有差異,因為停用圍欄是直接記憶體存取 (DMA) 顯示記憶體的結尾,但實際的顯示器切換和硬體 VSync 會在稍後發生。

「PRESENT_TIME_OFFSET_FROM_VSYNC_NS」已在裝置的 BoardConfig.mk makefile 中設定。這取決於螢幕控制器和面板特性。從退場柵欄時間戳記到硬體 VSync 信號的時間,以奈秒為單位。

VSYNC 和 SF_VSYNC 偏移

VSYNC_EVENT_PHASE_OFFSET_NS 和 SF_VSYNC_EVENT_PHASE_OFFSET_NS 是根據高負載使用案例保守設定,例如視窗轉換期間的部分 GPU 合成,或是 Chrome 捲動含有動畫的網頁。這些偏移量可讓應用程式轉譯時間和 GPU 合成時間較長。

延遲時間超過一到兩毫秒就會很明顯。如要盡量縮短延遲時間,同時避免錯誤次數大幅增加,請整合完整的自動錯誤測試。