Le signal VSync synchronise le pipeline d'affichage. Le pipeline d'affichage se compose du rendu de l'application, de la composition SurfaceFlinger et du Hardware Composer (HWC) qui présente les images sur l'écran. VSync synchronise le moment où les applications se réveillent pour commencer le rendu, le moment où SurfaceFlinger se réveille pour composer l'écran et le cycle d'actualisation de l'écran. Cette synchronisation élimine les saccades et améliore les performances visuelles des graphismes.

Le HWC génère des événements VSync et les envoie à SurfaceFlinger via le rappel :

typedef void (*HWC2_PFN_VSYNC)(hwc2_callback_data_t callbackData, hwc2_display_t display, int64_t timestamp);

SurfaceFlinger contrôle si le HWC génère ou non des événements VSync en appelant setVsyncEnabled. SurfaceFlinger permet à setVsyncEnabled de générer des événements VSync afin de pouvoir se synchroniser avec le cycle d'actualisation de l'écran. Lorsque SurfaceFlinger est synchronisé avec le cycle d'actualisation de l'écran, il désactive setVsyncEnabled pour empêcher le HWC de générer des événements VSync. Si SurfaceFlinger détecte une différence entre le VSync réel et celui qu'il a établi précédemment, il réactive la génération d'événements VSync.

Décalages VSync

L'application de synchronisation et les boucles de rendu SurfaceFlinger sont synchronisées avec le VSync matériel. Lors d'un événement VSync, l'écran commence à afficher le frame N tandis que SurfaceFlinger commence à composer les fenêtres pour le frame N+1. L'application gère les entrées en attente et génère le frame N+2.

La synchronisation avec VSync offre une latence constante. Il réduit les erreurs dans les applications et SurfaceFlinger, et minimise le déphasage des écrans. Cela suppose que les temps par frame de l'application et de SurfaceFlinger ne varient pas beaucoup. La latence est d'au moins deux images.

Pour y remédier, vous pouvez utiliser des décalages VSync afin de réduire la latence entre l'entrée et l'affichage en rendant les signaux d'application et de composition relatifs au VSync matériel. Cela est possible, car la composition de l'application prend généralement moins de 33 ms.

Le résultat d'un décalage VSync est constitué de trois signaux avec la même période et la même phase de décalage :

HW_VSYNC_0: l'écran commence à afficher l'image suivante.VSYNC: l'application lit l'entrée et génère le frame suivant.SF_VSYNC: SurfaceFlinger commence la composition pour le prochain frame.

Avec les décalages VSync, SurfaceFlinger reçoit le tampon et compose le frame tandis que l'application traite simultanément l'entrée et affiche le frame.

DispSync

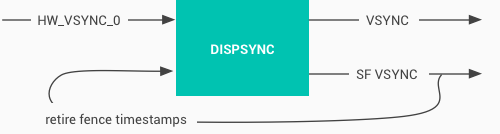

DispSync gère un modèle des événements VSync périodiques basés sur le matériel d'un écran et l'utilise pour exécuter des rappels à des décalages de phase spécifiques par rapport aux événements VSync matériels.

DispSync est une boucle à verrouillage de phase (PLL) logicielle qui génère les signaux VSYNC et SF_VSYNC utilisés par Choreographer et SurfaceFlinger, même s'ils ne sont pas décalés par rapport à la synchronisation verticale matérielle.

Le flux DispSync est illustré dans la figure suivante :

Figure 1 : Flux DispSync.

DispSync présente les qualités suivantes :

- Référence :

HW_VSYNC_0. - Sortie :

VSYNCetSF_VSYNC. - Feedback : supprimez les codes temporels des signaux de clôture du HWC.

Décalages de retrait VSync

Le code temporel du signal des barrières de retrait doit correspondre à la synchronisation verticale matérielle, même sur les appareils qui n'utilisent pas la phase de décalage. Sinon, les erreurs semblent plus graves qu'elles ne le sont. Les panneaux intelligents ont souvent un delta où la clôture de mise hors service correspond à la fin de l'accès direct à la mémoire (DMA) pour afficher la mémoire, mais le changement d'affichage réel et la synchronisation verticale matérielle se produisent quelque temps plus tard.

PRESENT_TIME_OFFSET_FROM_VSYNC_NS est défini dans le fichier make BoardConfig.mk de l'appareil. Elle est basée sur les caractéristiques du contrôleur et du panneau d'affichage. Le temps écoulé entre le code temporel de la barrière de retrait et le signal VSync matériel est mesuré en nanosecondes.

Décalages VSYNC et SF_VSYNC

VSYNC_EVENT_PHASE_OFFSET_NS et SF_VSYNC_EVENT_PHASE_OFFSET_NS sont définis de manière conservatrice en fonction des cas d'utilisation à forte charge, tels que la composition GPU partielle lors de la transition de fenêtre ou le défilement Chrome sur une page Web contenant des animations. Ces décalages permettent de longs temps de rendu d'application et de composition du GPU.

Une latence de plus d'une ou deux millisecondes est perceptible. Pour minimiser la latence sans augmenter de manière significative le nombre d'erreurs, intégrez des tests d'erreur automatisés complets.